|

SENMap: Multi-objective dataflow mapping & synthesis for hybrid scalable neuromorphic systems

Prithvish V N,

Oliver Rhodes,

Guangzhi Tang,

Alexandra Dobrita,

Yingfu Xu,

Kanishkan Vadivel,

Kevin Shidqi,

Paul Detterer,

Mario Konijnenburg,

Gert-Jan van Schaik,

Manolis Sifalakis,

Zaid Al-Ars,

Amirreza Yousefzadeh.

IEEE IJCNN

Abstract

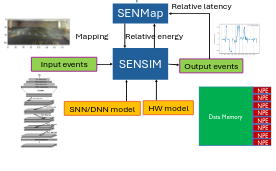

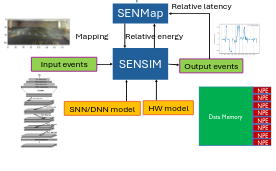

This paper introduces SENMap, a mapping and synthesis tool for scalable, energy-efficient neuromorphic computing architecture frameworks. SENECA is a flexible architectural design optimized for executing edge AI SNN/ANN inference applications efficiently. To speed up the silicon tapeout and chip design for SENECA, an accurate emulator, SENSIM, was designed. While SENSIM supports direct mapping of SNNs on neuromorphic architectures, as the SNN/ANNs grow in size, achieving optimal mapping for objectives like energy, throughput, area, and accuracy becomes challenging. This paper introduces SENMap, flexible mapping software for efficiently mapping large SNN/ANN applications onto adaptable architectures. SENMap considers architectural, pretrained SNN/ANN realistic examples, and event rate-based parameters and is open-sourced along with SENSIM to aid flexible neuromorphic chip design before fabrication. Experimental results show SENMap enables 40 percent energy improvements for a baseline SENSIM operating in timestep asynchronous mode of operation. SENMap is designed in such a way that it facilitates mapping large spiking neural networks for future modifications of SENeCA as well.

|

|

SENSIM: An Event-driven Parallel Simulator for Multi-core Neuromorphic Systems

Prithvish V N,

Mohammad Tahghighi,

Gert-Jan van Schaik,

Kanishkan Vadivel,

Manolis Sifalakis,

Guangzhi Tang,

Zaid Al-Ars.

Amirreza Yousefzadeh.

IEEE WCCI International Joint Conference on Neural Networks (IJCNN 2024)

Abstract | Paper | Video | Poster | slides

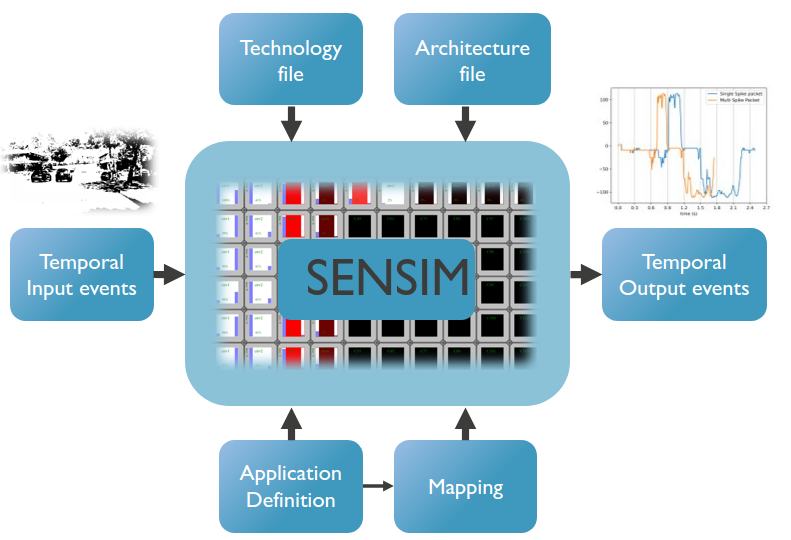

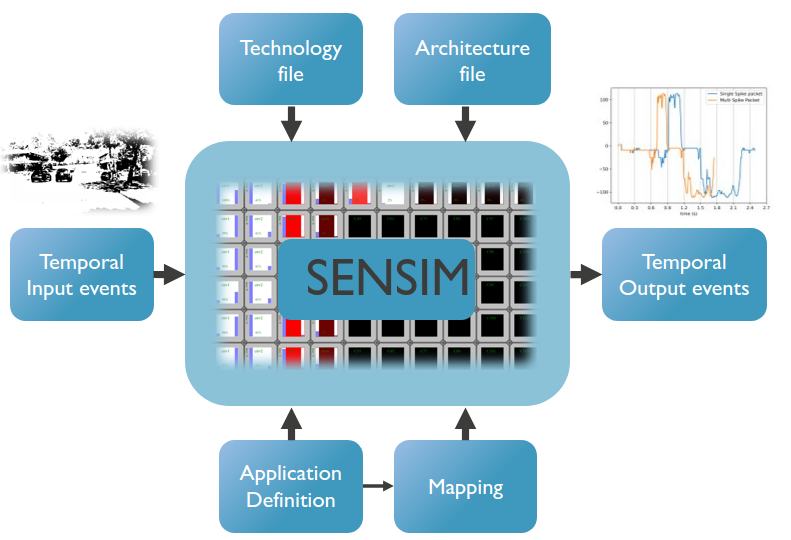

In this paper, we present SENSIM, which is an open-source simulator designed specifically for the SENECA neuromorphic processor. This simulator is unique in that it combines features from both hardware-specific and hardware-agnostic spiking neural network simulators, resulting in a hybrid event-driven and time-step-driven simulation approach. This allows for flexibility between accuracy and speed during different stages of simulation. Our work highlights the open-source SENSIM platform, which enables the mapping of large-scale SNN/DNN models to the SENECA cores, as well as the benchmarking of crucial KPIs such as power and latency estimations.

|

|

Optimizing event-based neural networks on digital neuromorphic architecture: a comprehensive design space exploration

Yingfu Xu,

Gert-Jan van Schaik,

Refik Bilgic,

Kevin Shidqi,

Alexandra Dobrita,

Shenqi Wang,

Roy Meijer,

Prithvish V N,

Cina Arjmand,

Pietro Martinello,

Anteneh Gebregiorgis,

Said Hamdioui,

Paul Detterer,

Stefano Traferro,

Mario Konijnenburg,

Kanishkan Vadivel,

Manolis Sifalakis,

Guangzhi Tang,

Amirreza Yousefzadeh.

Frontiers of Neuroscience Volume 18 (2024)

Abstract | Paper

Neuromorphic processors promise low-latency and energy-efficient processing by adopting novel brain-inspired design methodologies. Yet, current neuromorphic solutions still struggle to rival conventional deep learning accelerators' performance and area efficiency in practical applications. Event-driven data-flow processing and near/in-memory computing are the two dominant design trends of neuromorphic processors. However, there remain challenges in reducing the overhead of event-driven processing and increasing the mapping efficiency of near/in-memory computing, which directly impacts the performance and area efficiency. In this work, we discuss these challenges and present our exploration of optimizing event-based neural network inference on SENECA, a scalable and flexible neuromorphic architecture. To address the overhead of event-driven processing, we perform comprehensive design space exploration and propose spike-grouping to reduce the total energy and latency. Furthermore, we introduce the event-driven depth-first convolution to increase area efficiency and latency in convolutional neural networks (CNNs) on the neuromorphic processor. We benchmarked our optimized solution on keyword spotting, sensor fusion, digit recognition and high resolution object detection tasks. Compared with other state-of-the-art large-scale neuromorphic processors, our proposed optimizations result in a 6× to 300× improvement in energy efficiency, a 3× to 15× improvement in latency, and a 3× to 100× improvement in area efficiency. Our optimizations for event-based neural networks can be potentially generalized to a wide range of event-based neuromorphic processors.

|

|

Efficient mapping of large scale SNN and rate-based DNN on SENeCA

Prithvish V N,

Delft University of Technology, Library

Abstract | Master Thesis

Artificial intelligence, machine learning, and deep learning have been the buzzwords in almost every industry (medical, automotive, defense, security, finance, etc.) for the last decade. As the market moves towards AI-based solutions, so does the computation need for these solutions increase and change with time. With the rise of smart cities and cyberphysical systems, the need for edge devices and efficient computation on the edge increases. While most of these newly developed deep learning models are quite large and wasteful in terms of energy, there have been recent methods that help improve the performance on the edge. However, due to their size, variety, and irregularity, the computing and power requirements are often too large to deploy these models on edge devices. This prohibits the application of such models within a rich field of application that requires high-throughput and real-time execution.

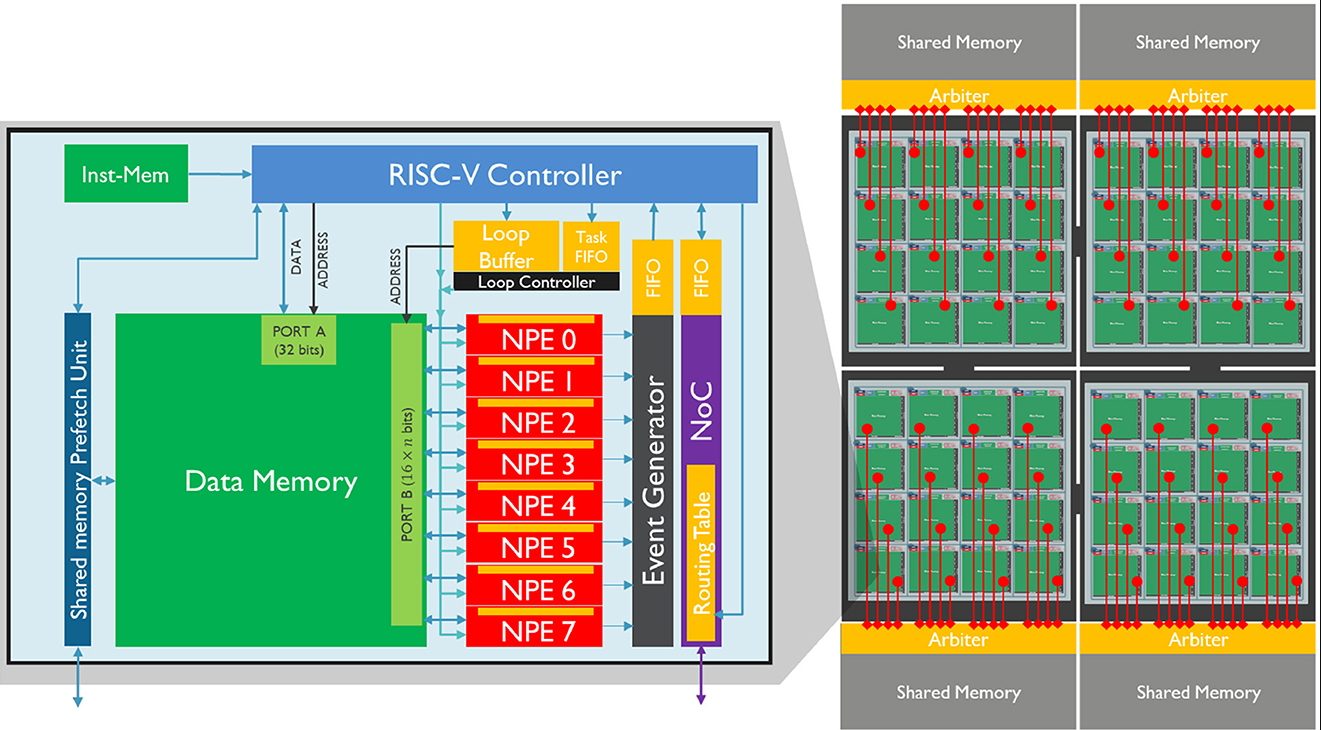

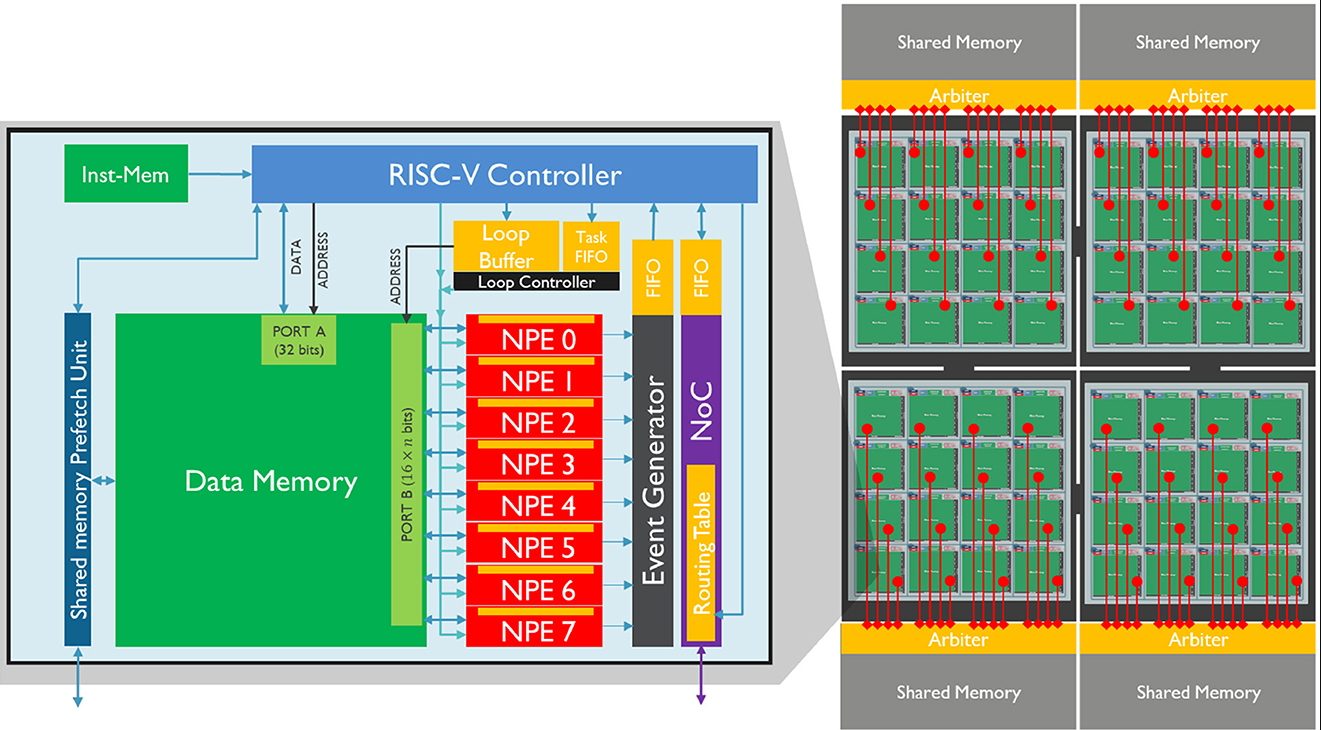

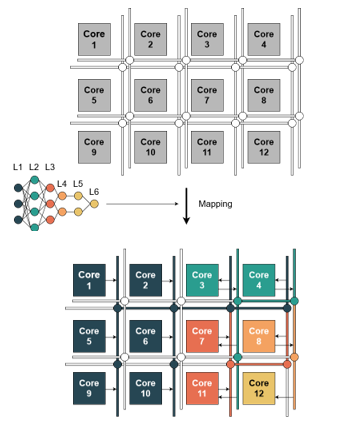

SENeCA (Scalable Energy Efficient Neuromorphic Computing Architecture) is a next-generation RISC-V-based neuromorphic computing architecture that was designed primarily for ultralow-edge applications where adaptivity is required. To mathematically model SENeCA, SENSIM (Scalable Energy Efficient Simulator, an open source simulator developed by the Interuniversity Microelectronic Center) provides an accurate mathematical software model of SENeCA, which helps in the early development and realization of a spiking neural network and deep neural network. This thesis work develops an efficient mapping tool SENMap (Scalable Energy-Efficient Neuromorphic Computing Architecture Mapper) on top of SENSIM which maps spiking neural networks efficiently. Having a faster, scalable realization software solution that can cater to large-scale neural networks can speed up the development procedure.

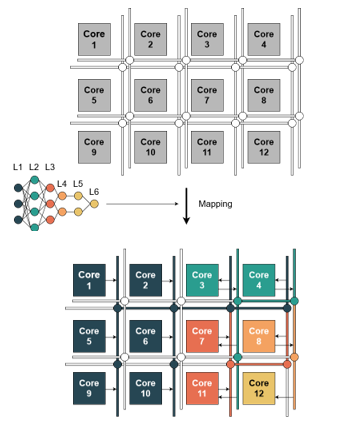

SENMap is developed in such a way that it supports flexible SNN/DNN application replacement, multiple single- and multi-objective optimization algorithms; the flexibility to choose from different optimization strategies; and also varying architectural parameters at the time of experimentation. Results show that mapping and neural processing elements (NPEs) depend primarily on the rate at which the sensor processes the data. On the basis of the rate, an early realization of SNN- and DNN-based edge AI chips SENMap. Depending on the actual parameters used, the maximum achieved improvements in energy consumption was around ~40%.

|